# EE 330 Lecture 19

Bipolar Device Operation and Modeling

#### Fall 2024 Exam Schedule

Exam 1 Friday Sept 27

Exam 2 Friday October 25

Exam 3 Friday Nov 22

Final Exam Monday Dec 16 12:00 - 2:00

PM

#### **Review from last lecture**

TABLE 2B.1

Process scenario of major process steps in typical n-well CMOS process<sup>a</sup>

| 1.  | Clean wafer                                                     |            |

|-----|-----------------------------------------------------------------|------------|

| 2.  | GROW THIN OXIDE                                                 |            |

| 3.  | Apply photoresist                                               |            |

| 4.  | PATTERN n-well                                                  | (MASK #1)  |

| 5.  | Develop photoresist                                             |            |

| 6.  | Deposit and diffus n-type impurities                            |            |

| 7.  | Strip photoresist                                               |            |

| 8.  | Strip thin oxide                                                |            |

| 9.  | Grow thin oxide                                                 |            |

| 10. | Apply layer of Si <sub>3</sub> N <sub>4</sub>                   |            |

| 11. | Apply photoresist                                               |            |

| 12. | PATTERN Si <sub>3</sub> N <sub>4</sub> (active area definition) | (MASK #2)  |

| 13. | Develop photoresist                                             |            |

| 14. | Etch Si <sub>3</sub> N <sub>4</sub>                             |            |

| 15. | Strip photoresist                                               |            |

|     | Optional field threshold voltage adjust                         |            |

|     | A.1 Apply photoresist                                           |            |

|     | A.2 PATTERN ANTIMOAT IN SUBSTRATE                               | (MASK #A1) |

|     | A.3 Develop photoresist                                         |            |

|     | A.4 FIELD IMPLANT p-type)                                       |            |

|     | A.5 Strip photoresist                                           |            |

| 16. | GROW FIELD OXIDE                                                |            |

| 17. | Strip Si <sub>3</sub> N <sub>4</sub>                            |            |

| 18. | Strip thin oxide                                                |            |

| 19. | GROW GATE OXIDE                                                 |            |

| 20. | POLYSILICON DEPOSITION (POLY I)                                 |            |

| 21. | Apply photoresist                                               | -          |

| 22. | PATTERN POLYSILICON                                             | (MASK #3)  |

| 23. | Develop photoresist                                             |            |

| 24. | ETCH POLYSILICON                                                |            |

#### **Review from last lecture**

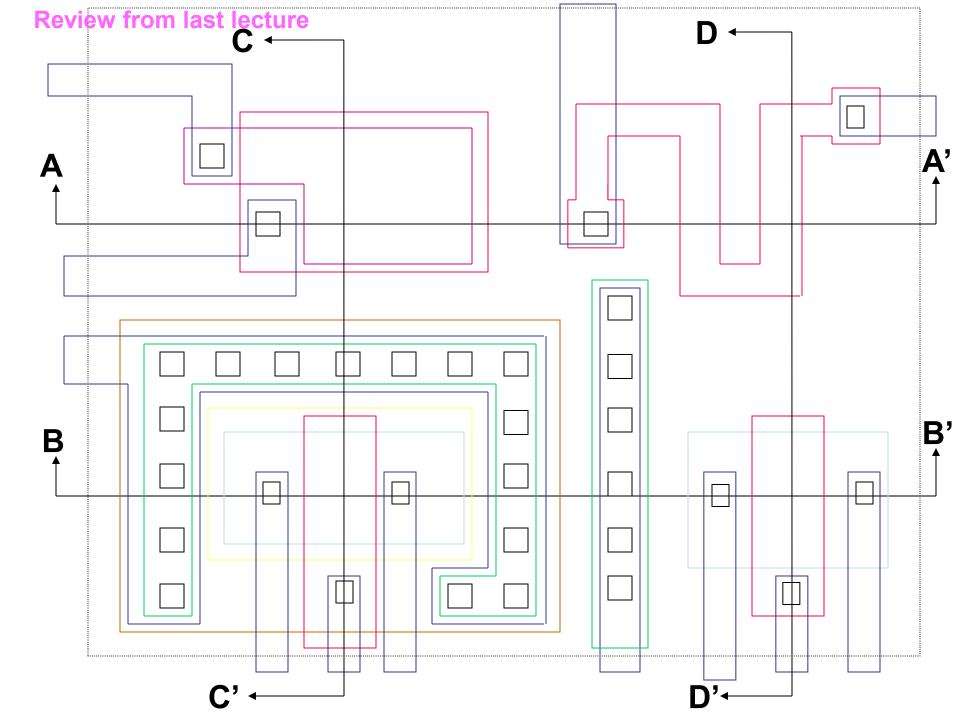

#### **Metal Mask**

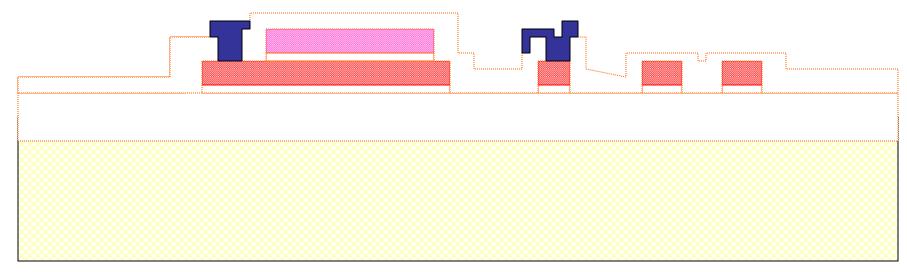

**A-A' Section**

**B-B' Section**

#### **Review from last lecture**

#### Should now know what you can do in this process !!

Can metal connect to active?

Can metal connect to substrate when on top of field oxide?

How can metal be connected to substrate?

Can poly be connected to active under gate?

Can poly be connected to active any place?

Can metal be placed under poly to isolate it from bulk?

Can metal 2 be connected directly to active?

Can metal 2 be connected to metal 1?

Can metal 2 pass under metal 1?

Could a process be created that will result in an answer of YES to most of above?

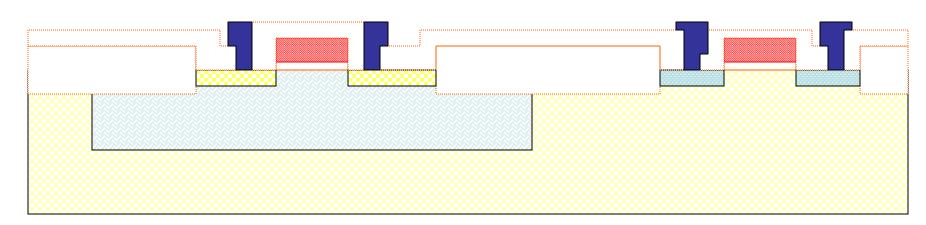

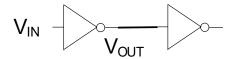

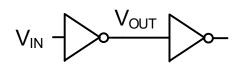

How does the minimum-sized inverter delay when driving an identical device compare between a 0.5u process and a 0.18u process?

How does the minimum-sized inverter delay when driving an identical device compare between a 0.5u process and a 0.18u process?

$$V_{IN}$$

$V_{OUT}$

Recall:

$$C_{IN} = C_{GSn} + C_{GSp}$$

$$\begin{aligned} &t_{\text{HL}} = &R_{\text{PD}} C_{\text{IN}} \\ &t_{\text{LH}} = &R_{\text{PU}} C_{\text{IN}} \\ &t_{\text{PROP}} = &t_{\text{HL}} + &t_{\text{LH}} \end{aligned}$$

How does the minimum-sized inverter delay when driving an identical device compare between a 0.5u process and a 0.18u process?

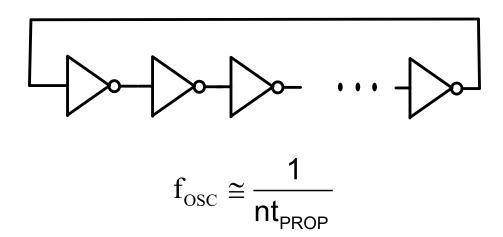

It will also be shown later that if n inverters are connected in a loop and if n is odd, this will form a "ring" oscillator:

RUN: T91T

TECHNOLOGY: SCN05

VENDOR: AMIS

EATURE SIZE: 0.5 microns

Run type: SKD

INTRODUCTION: This report contains the lot average results obtained by MOSIS from measurements of MOSIS test structures on each wafer of this fabrication lot. SPICE parameters obtained from similar

measurements on a selected wafer are also attached.

COMMENTS: American Microsystems, Inc. C5

| TRANSISTOR PARAMETERS                  | W/L       | N-CHANNEL                    | P-CHANNEL                       | UNITS                         |

|----------------------------------------|-----------|------------------------------|---------------------------------|-------------------------------|

| МІНІМИM<br>Vth                         | 3.0/0.6   | 0.81                         | -0.92                           | volts                         |

| SHORT<br>Idss<br>Vth<br>Vpt            | 20.0/0.6  | 466<br>0.69<br>12.7          | -250<br>-0.89<br>-11.7          | uA/um<br>volts<br>volts       |

| WIDE<br>Ids0                           | 20.0/0.6  | < 2.5                        | < 2.5                           | pA/um                         |

| LARGE<br>Vth<br>Vjbkd<br>Ijlk<br>Gamma | 20.0/20.0 | 0.71<br>8.8<br><50.0<br>0.44 | -0.94<br>-11.7<br><50.0<br>0.57 | volts<br>volts<br>pA<br>V^0.5 |

| K' (Vo*Cox/2)<br>Low-field Mobility    |           | 54.8<br>434.84               | -19.7<br>156.32                 | uA/V^2<br>cm^2/V*s            |

| PROCESS PARAMETERS     | N+         | <b>P</b> + | POLY     | PLY2_HR | M1   | UNITS     |

|------------------------|------------|------------|----------|---------|------|-----------|

| Sheet Resistance       | 85.3       | 111.2      | 22.4     | 1033    | 0.09 | ohms/sq   |

| Contact Resistance     | 59.6       | 145.4      | 17.9     |         |      | ohms      |

| Gate Oxide Thickness   | 137        |            |          |         |      | angstroms |

|                        |            |            |          |         |      |           |

| CAPACITANCE PARAMETERS | <b>N</b> + | <b>P</b> + | POLY     | POLY2   | м1   | UNITS     |

| Area (substrate)       | 443        | 745        | 102      |         |      | aF/um^2   |

| Area (N+active)        |            |            | 2518     |         |      | aF/um^2   |

| Area (P+active)        |            |            | 2441     |         |      | aF/um^2   |

| Area (poly)            |            |            |          | 896     | 61   | aF/um^2   |

|                        |            |            |          |         |      |           |

| CIRCUIT PARAMETERS     |            |            | ****     |         |      |           |

| CIRCUIT PARAMETERS     |            |            | UNIT     | r's     |      |           |

| Ring Oscillator Freq.  | _          | 0.4        | 47 301   |         |      |           |

| DIV256 (31-stg,5.0V)   |            | 94         | .47 MHz  |         |      |           |

| Ring Oscillator Power  |            |            | 40 -776  | mr_ / t |      |           |

| DIV256 (31-stg,5.0V)   |            | U          | .48 uW/M | Mz/gate |      |           |

\_\_\_\_\_

#### MOSIS WAFER ACCEPTANCE TESTS

RUN: T4BK (MM\_NON-EPI\_THK-MTL)

TECHNOLOGY: SCN018 FEATURE SIZE: 0.18 microns

INTRODUCTION: This report contains the lot average results obtained by MOSIS

from measurements of MOSIS test structures on each wafer of this fabrication lot. SPICE parameters obtained from similar

VENDOR: TSMC

measurements on a selected wafer are also attached.

COMMENTS: DSCN6M018\_TSMC

| TRANSISTOR PARAMETERS | W/L       | N-CHANNE | EL P-CHANNEL | UNITS    |

|-----------------------|-----------|----------|--------------|----------|

| MINIMUM<br>Vth        | 0.27/0.18 | 0.5      | 50 -0.53     | volts    |

| VCII                  |           | <u> </u> | 0.33         | VOICS    |

| SHORT                 | 20.0/0.18 |          |              |          |

| Idss                  |           | 571      | -266         | uA/um    |

| Vth                   |           | 0.5      | -0.53        | volts    |

| Vpt                   |           | 4.7      | 7 -5.5       | volts    |

| WIDE                  | 20.0/0.18 |          |              |          |

| Ids0                  |           | 22.0     | -5.6         | pA/um    |

| LARGE                 | 50/50     |          |              |          |

| Vth                   |           | 0.4      | -0.41        | volts    |

| Vjbkd                 |           | 3.3      | l -4.1       | volts    |

| Ijlk                  |           | <50.6    | <50.0        | рΑ       |

| K' (Uo*Cox/2)         |           | 171.8    | 3 -36.3      | uA/V^2   |

| Low-field Mobility    |           | 398.0    | 92 84.10     | cm^2/V*s |

| CAPACITANCE PARAMETERS Area (substrate) Area (N+active) Area (P+active)                          |     | P+ POLY<br>1152 103<br>8566<br>8324 | 39 | 19         | 13       |                      | 8                    | M6<br>3<br>9  | R_W | D_N_W<br>129 | M5P  | N_W<br>127 | UNITS<br>aF/um^2<br>aF/um^2<br>aF/um^2   |

|--------------------------------------------------------------------------------------------------|-----|-------------------------------------|----|------------|----------|----------------------|----------------------|---------------|-----|--------------|------|------------|------------------------------------------|

| Area (poly) Area (metal1) Area (metal2)                                                          |     |                                     | 64 | 18<br>44   | 16       | 10<br>15             | 6<br>7<br>9          | 7             |     |              |      |            | aF/um^2<br>aF/um^2                       |

| Area (metal3)<br>Area (metal4)<br>Area (metal5)<br>Area (r well)                                 | 987 |                                     |    |            |          | 40                   | 15<br>37             | 9<br>14<br>36 |     |              | 1003 |            | aF/um^2<br>aF/um^2<br>aF/um^2<br>aF/um^2 |

| Area (d well)<br>Area (no well)                                                                  | 139 |                                     |    |            |          |                      |                      |               | 574 |              |      |            | aF/um^2<br>aF/um^2                       |

| Fringe (substrate) Fringe (poly) Fringe (metal1) Fringe (metal2) Fringe (metal3) Fringe (metal4) | 244 | 201                                 |    | 39         | 29<br>35 | 43<br>24<br>37<br>56 | 21<br>23<br>27<br>34 | 21<br>24      |     |              |      |            | aF/um aF/um aF/um aF/um aF/um aF/um      |

| Fringe (metal5)<br>Overlap (P+active)                                                            |     | 652                                 |    |            |          |                      |                      | 61            |     |              |      |            | aF/um<br>aF/um                           |

| CIRCUIT PARAMETERS                                                                               |     |                                     |    |            |          | UNI                  | ΓS                   |               |     |              |      |            |                                          |

| Inverters<br>Vinv                                                                                |     | K<br>1.0                            |    | a 7,       | 1        | volt                 | + c                  |               |     |              |      |            |                                          |

| Vinv                                                                                             |     | 1.5                                 |    |            |          | vol                  |                      |               |     |              |      |            |                                          |

| Vol (100 uA)                                                                                     |     | 2.0                                 |    |            |          | volt                 |                      |               |     |              |      |            |                                          |

| Voh (100 uA)                                                                                     |     | 2.0                                 |    |            |          | vol                  |                      |               |     |              |      |            |                                          |

| Vin∨<br>Gain                                                                                     |     | 2.0<br>2.0                          |    | 0.8<br>3.3 |          | volt                 | ts                   |               |     |              |      |            |                                          |

| Ring Oscillator Freq.                                                                            |     | 2.0                                 | 2  | ٠          | ,        |                      |                      |               |     |              |      |            |                                          |

| D1024_THK (31-s+g_3                                                                              | •   |                                     |    | R 2        |          | MHz                  | -                    |               |     |              |      |            |                                          |

| DIV1024 (31-stg,1.8V                                                                             |     |                                     | 40 | 2.84       | 4        | MHz                  | _                    |               |     |              |      |            |                                          |

| Ring Oscillator Power<br>D1024_THK (31-stg,3.<br>DIV1024 (31-stg,1.8V                            | 3V) |                                     |    | 0.0<br>0.0 |          | uW/I                 |                      |               |     |              |      |            |                                          |

How does the minimum-sized inverter delay compare between a 0.5u process and a 0.18u process?

| Feature | 0.5   | 0.18  | Units   |

|---------|-------|-------|---------|

|         |       |       |         |

| Vtn     | 0.81  | 0.5   | V       |

| Vtp     | -0.92 | -0.53 | V       |

| uCoxn   | 109.6 | 344   | uA/V^2  |

| иСохр   | 39.4  | 72.6  | uA/V^2  |

| Cox     | 2.51  | 8.5   | fF/µm^2 |

| Vdd     | 5     | 1.8   | V       |

|         |       |       |         |

| fosc-31 | 94.5  | 402.8 | MHz     |

Assume n-channel and p-channel devices with L=Lmin, W=1.5Lmin

$$t_{HL} = R_{pd}C_{L}$$

$$t_{LH} = R_{pd}C_{L}$$

$$R_{pd} = \frac{L_{n}}{\mu_{n}C_{OX}W_{n}(V_{DD} - V_{TN})}$$

$$R_{pu} = \frac{L_{p}}{\mu_{p}C_{OX}W_{p}(V_{DD} + V_{TP})}$$

Feature 0.5 0.18 Units

| $C_{L} = C_{OX} \left( W_{n} L_{n} + W_{p} L_{p} \right)$ | $C_L = C_{OX}$ | $(W_nL_n)$ | $+W_{\rho}L_{\rho}$ | ) |

|-----------------------------------------------------------|----------------|------------|---------------------|---|

|-----------------------------------------------------------|----------------|------------|---------------------|---|

|         |      |      | $\mu_{p}$ C <sub>DX</sub> VV <sub>p</sub> (V <sub>D1</sub> |

|---------|------|------|------------------------------------------------------------|

| Feature | 0.5  | 0.18 | Units                                                      |

| CL      | 1.88 | 0.83 | fF                                                         |

| Rpd     | 1452 | 1491 | ohms                                                       |

| Rpu     | 2858 | 3941 | ohms                                                       |

| THL     | 2.73 | 1.23 | psec                                                       |

| TLH     | 5.38 | 3.26 | psec                                                       |

| f       | 123  | 223  | GHz                                                        |

Note 0.18u process is much faster than 0.5u process Some scale even faster

#### Basic Devices and Device Models

- Resistor

- Diode

- Capacitor

- MOSET

- BJT

Lets pick up a discussion of Technology Files before moving to BJT

Return to basic devices!

#### **Basic Devices and Device Models**

- Resistor

- Diode

- Capacitor

- MOSFET

# **Bipolar Junction Transistors**

- Operation

- Modeling

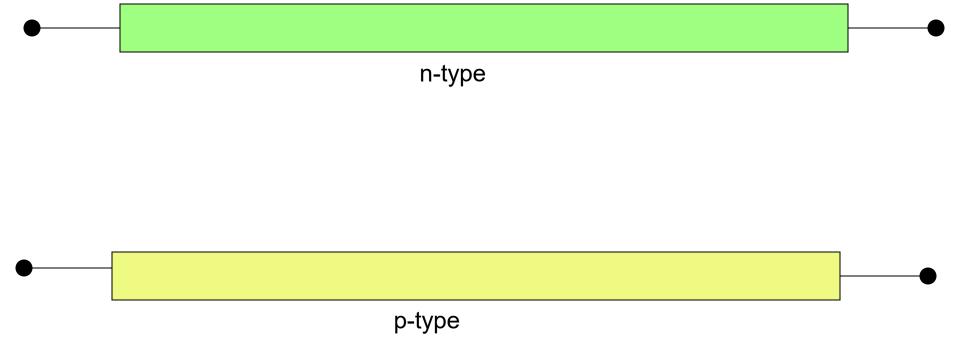

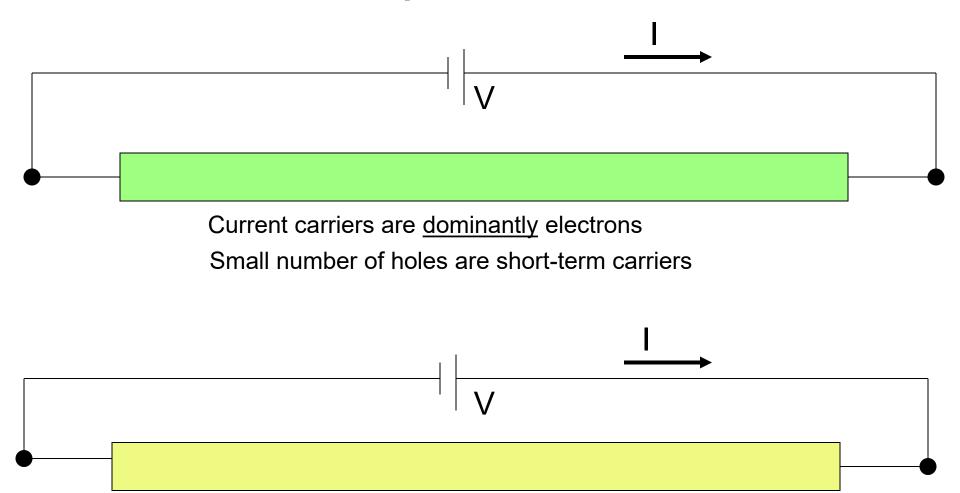

# Carriers in Doped Semiconductors

## Carriers in Doped Semiconductors

Current carriers are <u>dominantly</u> holes Small number of electrons are short-term carriers

# Carriers in Doped Semiconductors

|        | Majority<br>Carriers | Minority<br>Carriers |

|--------|----------------------|----------------------|

| n-type | electrons            | holes                |

| p-type | holes                | electrons            |

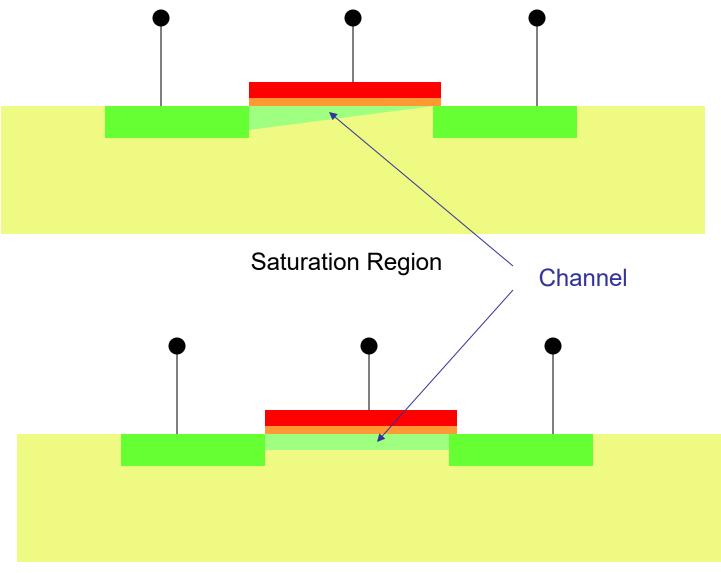

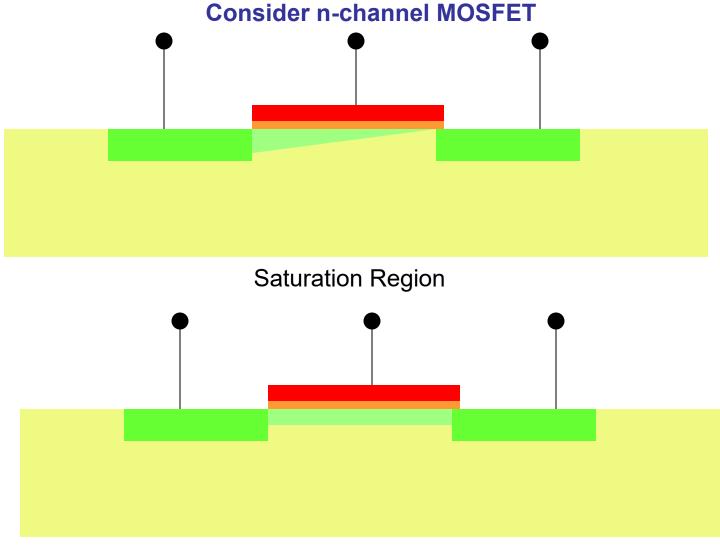

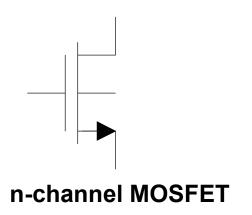

**Consider n-channel MOSFET**

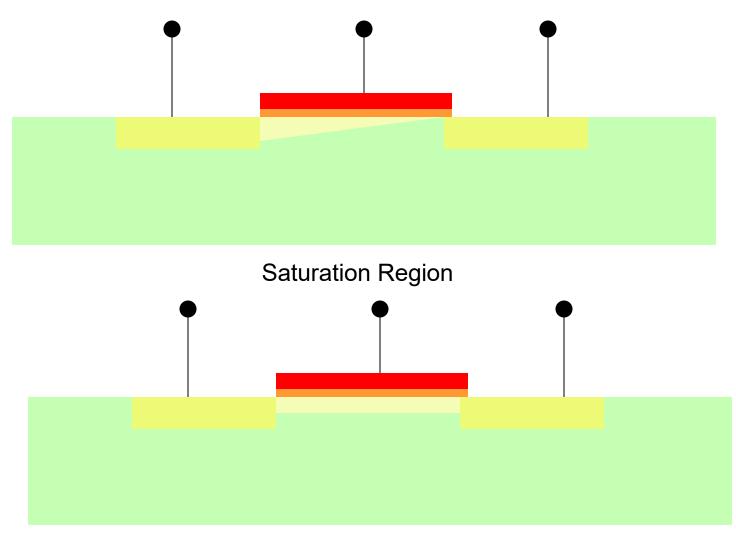

Triode Region

Triode Region

Carriers in electrically induced n-channel are electrons

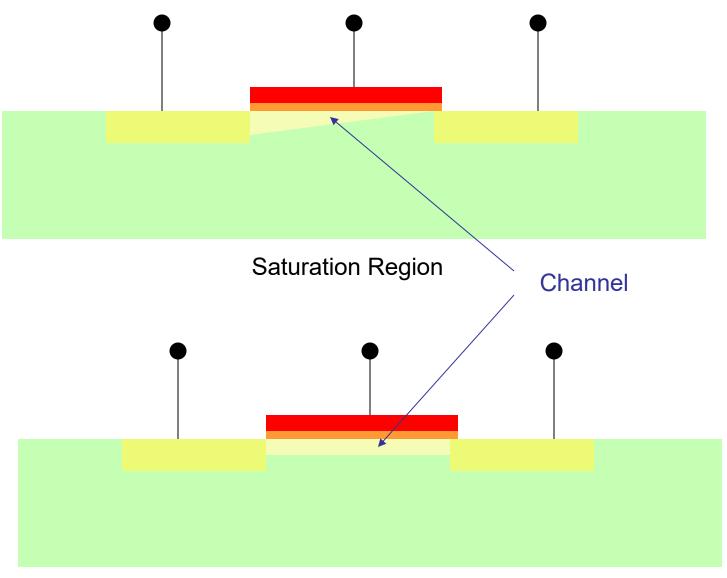

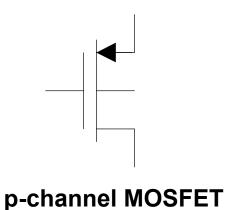

**Consider p-channel MOSFET**

Triode Region

**Consider p-channel MOSFET**

Triode Region

Carriers in electrically induced p-channel are holes

Carriers in channel of MOS transistors are Majority carriers

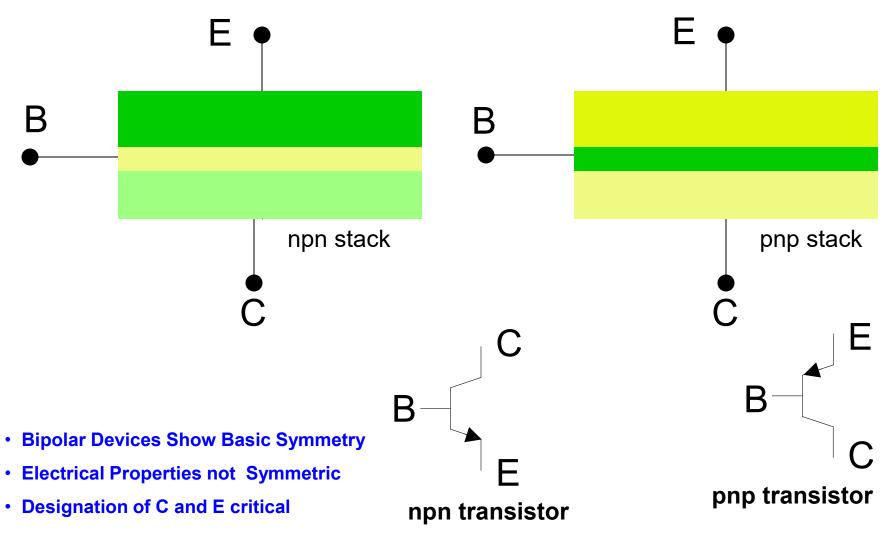

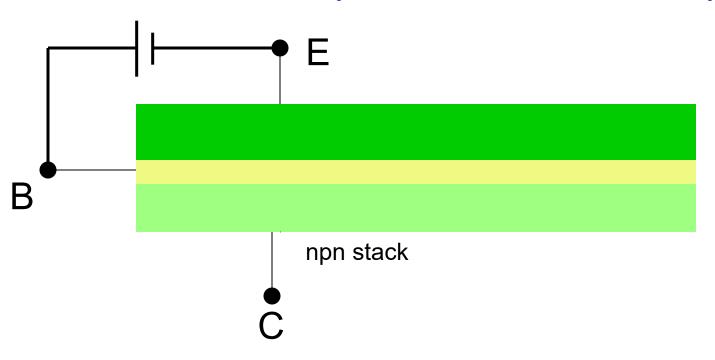

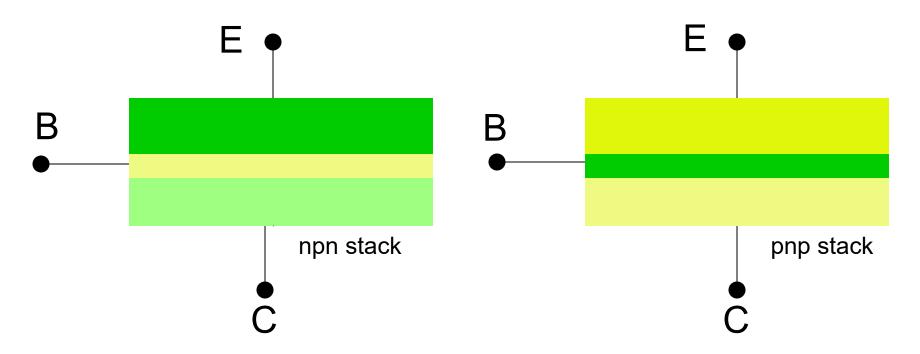

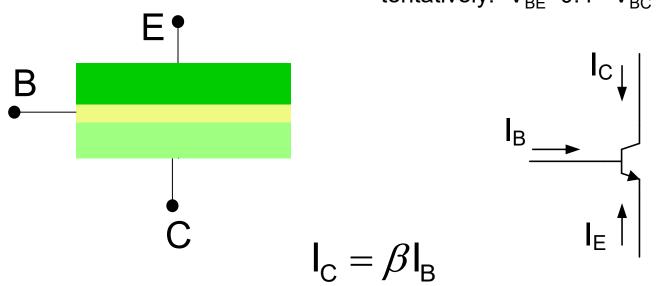

# **Bipolar Transistors**

With proper doping and device sizing these form Bipolar Transistors

# **Bipolar Transistors**

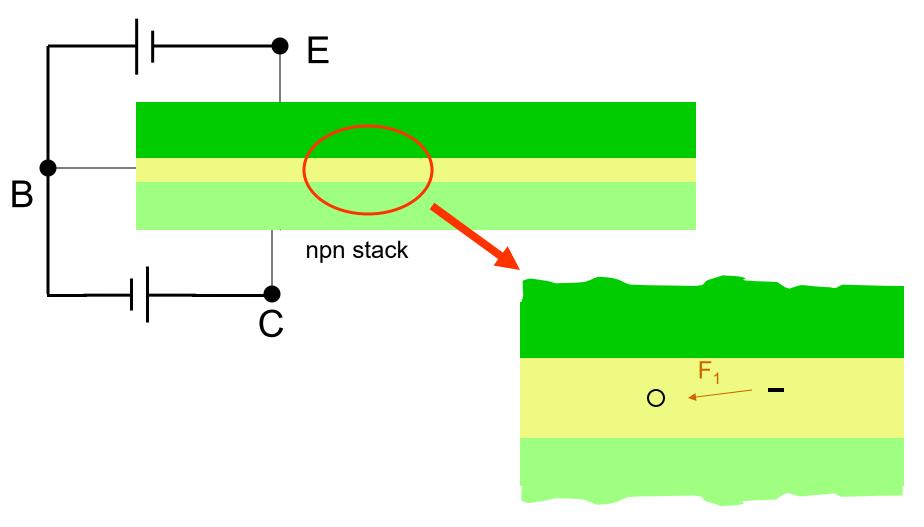

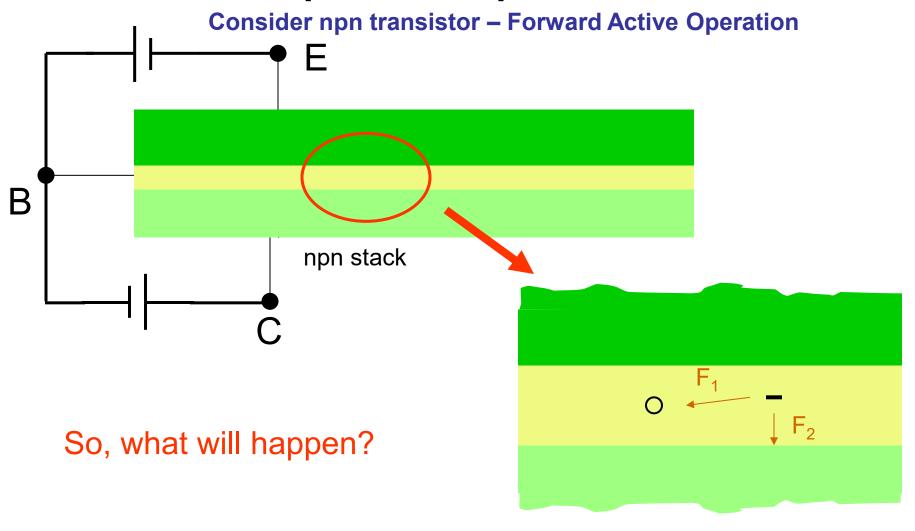

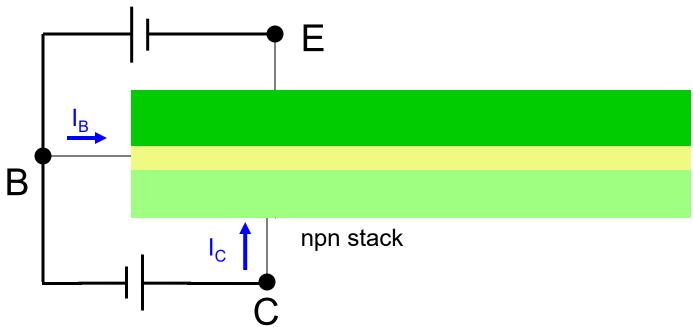

**Consider npn transistor – Forward Active Operation**

Under **forward BE bias** current flow into base and out of emitter

Current flow is governed by the diode equation

Carriers in emitter are electrons (majority carriers)

When electrons pass into the base they become minority carriers

Quickly recombine with holes to create holes in base region

Dominant current flow in base is holes (majority carriers)

# Bipolar Operation Consider npn transistor – Forward Active Operation

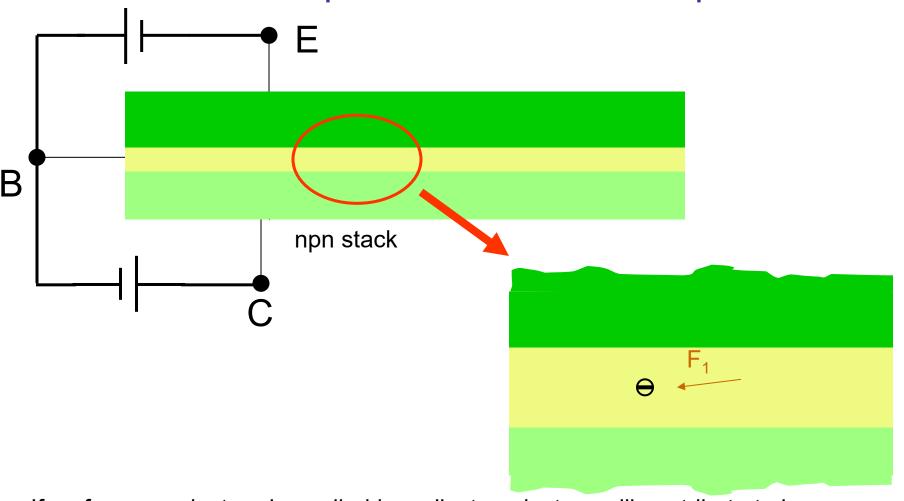

Under forward BE bias and reverse BC bias current flows into base region

Carriers in emitter are electrons (majority carriers)

When electrons pass into the base they become minority carriers

When minority carriers are present in the base they can be attracted to collector

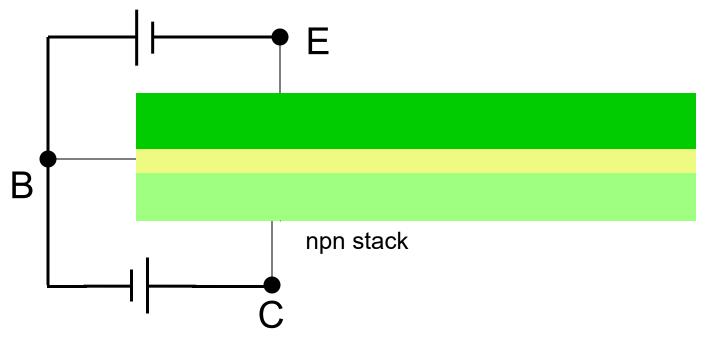

# Bipolar Operation Consider npn transistor – Forward Active Operation

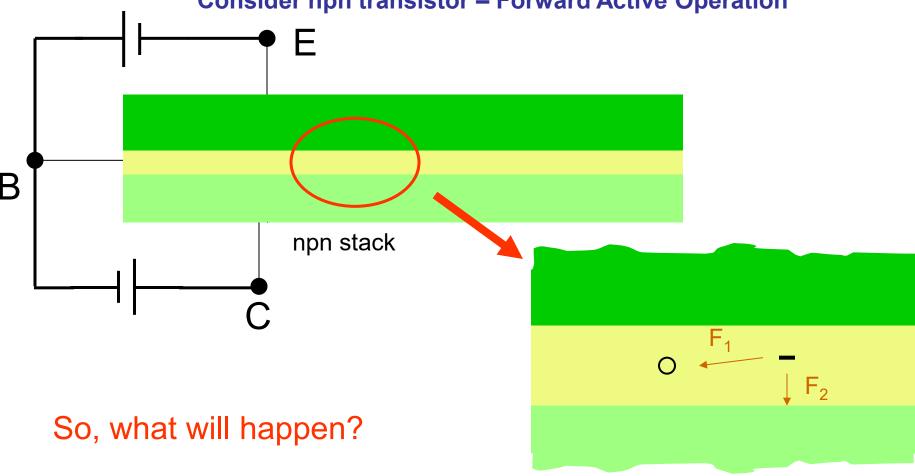

If no force on electron is applied by collector, electron will contribute to base current

**Consider npn transistor – Forward Active Operation**

If no force on electron is applied by collector, electron will contribute to base current Electron will recombine with a hole so dominant current flow in base will be by majority carriers

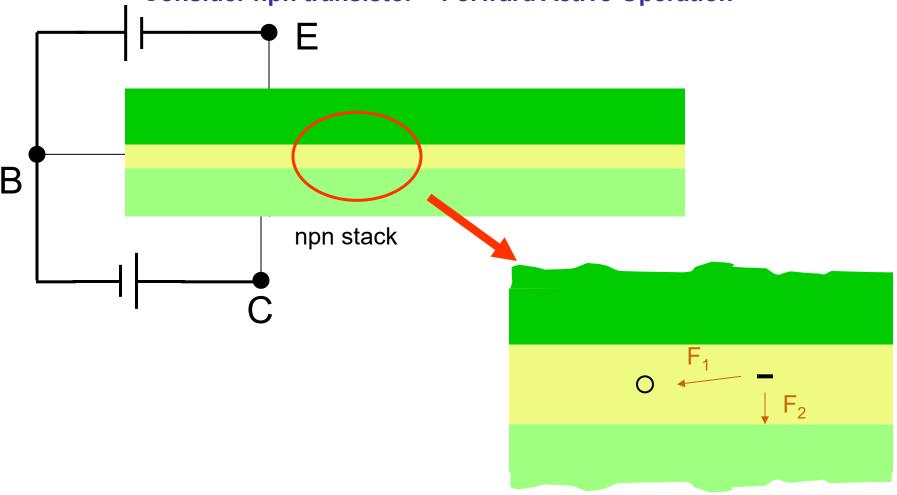

**Consider npn transistor – Forward Active Operation**

When minority carriers are present in the base they can be attracted to collector with reverse-bias of BC junction and can move across BC junction

**Consider npn transistor – Forward Active Operation**

When minority carriers are present in the base they can be attracted to collector with reverse-bias of BC junction and can move across BC junction

Will contribute to collector current flow as majority carriers

**Consider npn transistor – Forward Active Operation**

Some will recombine with holes and contribute to base current and some will be attracted across BC junction and contribute to collector

Size and thickness of base region and relative doping levels will play key role in percent of minority carriers injected into base contributing to collector current

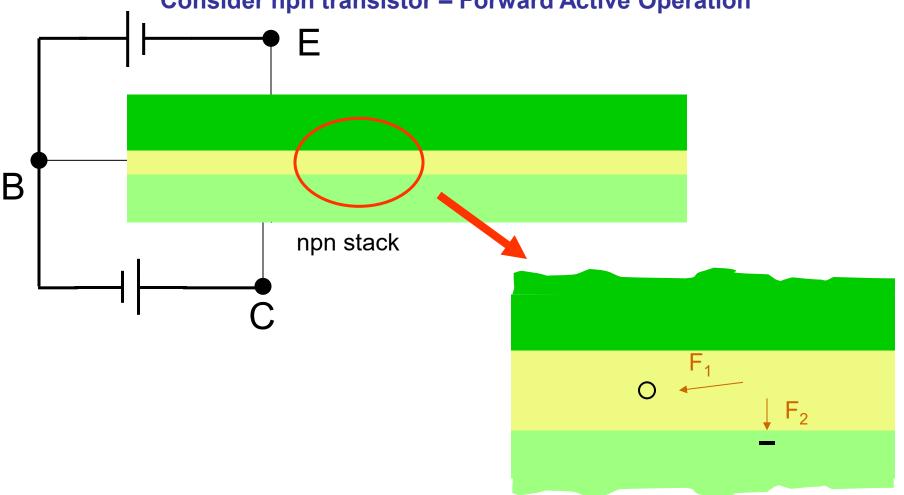

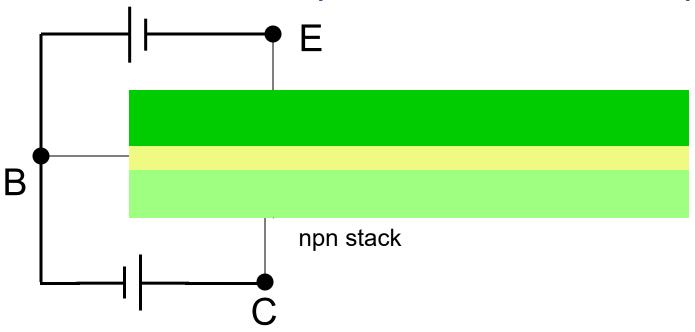

**Consider npn transistor – Forward Active operation**

Under forward BE bias and reverse BC bias current flows into base region

Carriers in emitter are electrons (majority carriers)

When electrons pass into the base they become minority carriers

When minority carriers are present in the base they can be attracted to collector

Minority carriers either recombine with holes and contribute to base current or are attracted into collector region and contribute to collector current

**Consider npn transistor – Forward Active operation**

Minority carriers either recombine with holes and contribute to base current or are attracted into collector region and contribute to collector current

If most of the minority carriers are attracted to collector,  $\left|\mathbf{I}_{c}\right|\simeq\left|\mathbf{I}_{E}\right|$  Thus  $\mathbf{I}_{B}\text{<<}\mathbf{I}_{C}$

Implications of this observation?

If input to device is I<sub>B</sub> and output is I<sub>C</sub>, the BJT will behave as a current amplifier with large current gain!! This was the key observation by Bell Labs in 1948!!

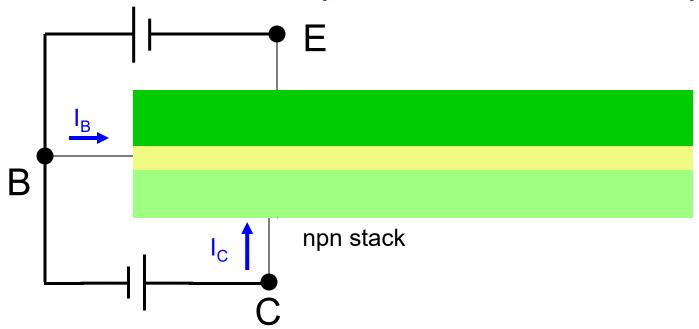

**Consider npn transistor - Forward Active Operation**

Under forward BE bias and reverse BC bias current flows into base region

- Efficiency at which minority carriers injected into base region and contribute to collector current is termed α

- α is always less than 1 but for a good transistor, it is very close to 1

- For good transistors  $.99 < \alpha < .999$

- Making the base region very thin makes α large

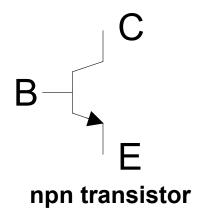

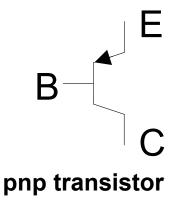

#### **Bipolar Transistors**

- principle of operation of pnp and npn transistors are the same

- minority carriers in base of pnp are holes

- npn usually have modestly superior properties because mobility of electrons is larger than mobility of holes

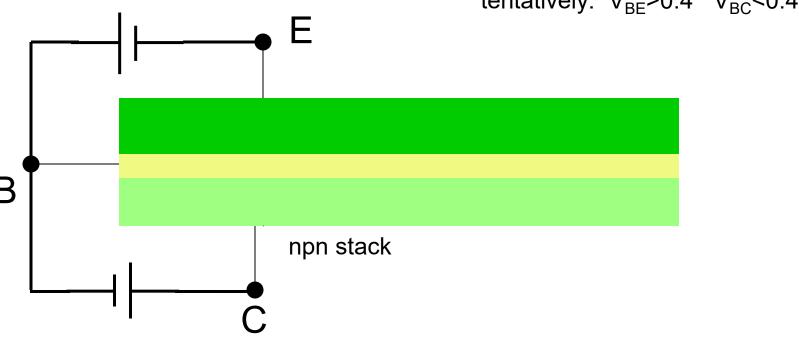

#### **Consider npn transistor – Forward Active Operation**

tentatively:  $V_{BE} > 0.4$   $V_{BC} < 0.4$

In contrast to MOS devices where current flow in channel is by majority carriers, current flow in the critical base region of bipolar transistors is by minority carriers

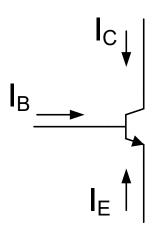

#### **Consider npn transistor – Forward Active Operation**

tentatively:  $V_{BF} > 0.4$   $V_{BC} < 0.4$

$$I_{C} + I_{B} = -I_{E}$$

$$I_{C} = -\alpha I_{E}$$

$$\beta = \frac{1-\alpha}{1-\alpha} I_{\rm B}$$

$$\beta = \frac{\alpha}{1-\alpha}$$

$$I_{C} = \beta I_{B}$$

$\beta$  is typically very large often 50< $\beta$ <999

#### **Consider npn transistor – Forward Active Operation**

tentatively:  $V_{BE} > 0.4$   $V_{BC} < 0.4$

β is typically very large

Bipolar transistor can be thought of as current amplifier with a large current gain In contrast, MOS transistor is inherently a tramsconductance amplifier  $V_{BE}$

Current flow in base is governed by the diode equation

Collector current thus varies exponentially with  $V_{\text{BE}}$

$$I_{C} = \beta \widetilde{I}_{S} e^{\frac{V_{BE}}{V_{t}}}$$

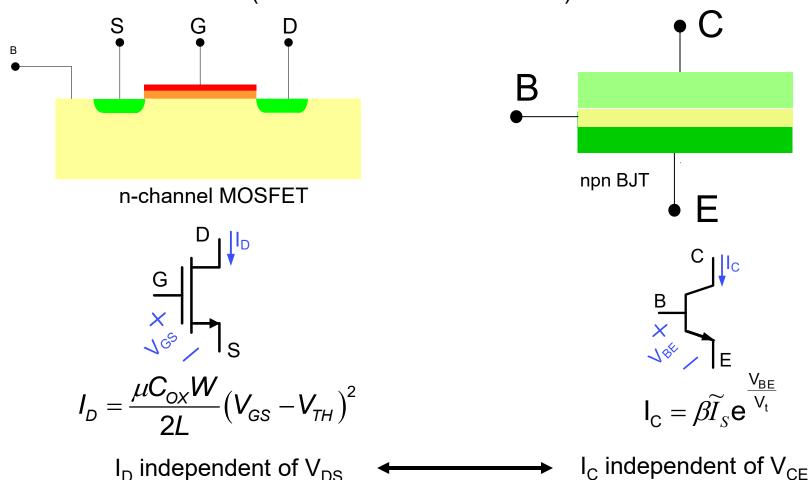

#### Preliminary Comparison of MOSFET and BJT

(Saturation vs Forward Active)

- The BJT I/O relationship is exponential in contrast to square-law for MOSFET

- Provides a very large "gain" for the BJT (assuming input is voltage and output is current)

- This property is very useful for many applications

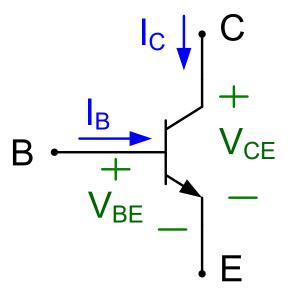

## Bipolar Models

Simple dc Model

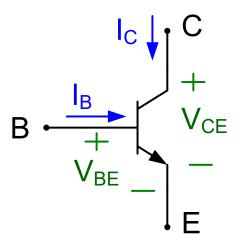

Following convention, pick  $I_C$  and  $I_B$  as dependent variables and  $V_{EE}$  and  $V_{CE}$  as independent variables

**Consider npn transistor – Forward Active Operation**

Summary:

$$\mathbf{I}_{\mathsf{B}} = \widetilde{I}_{S} \mathbf{e}^{\frac{\mathsf{V}_{\mathsf{BE}}}{\mathsf{V}_{\mathsf{t}}}}$$

$$\mathbf{I}_{\mathsf{C}} = \beta \widetilde{I}_{S} \mathbf{e}^{\frac{\mathsf{V}_{\mathsf{BE}}}{\mathsf{V}_{\mathsf{t}}}}$$

$$\mathsf{V}_{\mathsf{t}} = \frac{\mathsf{kT}}{\mathsf{a}}$$

This has the properties we are looking for but the variables we used in introducing these relationships are not standard

It can be shown that  $\widetilde{I}_S$  is proportional to the emitter area  $\mathsf{A}_\mathsf{E}$

Define  $J_s$  by  $\widetilde{I}_s = \beta^{-1} J_s A_E$  and substitute this into the above equations

npn transistor – Forward Active Operation

$$I_{B} = \widetilde{I}_{S} e^{\frac{V_{BE}}{V_{t}}}$$

$$I_{C} = \beta \widetilde{I}_{S} e^{\frac{V_{BE}}{V_{t}}}$$

$$V_{C} = \frac{kT}{q}$$

$$I_{C} = 8.62 \times 10^{-5}$$

$$I_{C} = Forward Active Operation

$$I_{B} = \frac{J_{S}A_{E}}{\beta} e^{\frac{V_{BE}}{V_{t}}}$$

$$I_{C} = J_{S}A_{E} e^{\frac{V_{BE}}{V_{t}}}$$

$$V_{C} = \frac{kT}{q}$$

$$V_{C} = \frac{kT}{q}$$

$$V_{C} = \frac{kT}{q}$$$$

**Standard Notation:**  $\beta$  moved to  $I_C$  equation

J<sub>S</sub> is termed the saturation current density

Process Parameters :  $J_S,\beta$

Design Parameters: A<sub>F</sub>

Environmental parameters and physical constants: k,T,q

At room temperature, V<sub>t</sub> is around 26mV

J<sub>S</sub> very small – around .25fA/u<sup>2</sup> at room temperature

npn transistor - Forward Active Operation

$$I_{B} = \frac{J_{S}A_{E}}{\beta}e^{\frac{V_{BE}}{V_{t}}}$$

$$I_{C} = J_{S}A_{E}e^{\frac{V_{BE}}{V_{t}}}$$

$$V_{t} = \frac{kT}{\alpha}$$

As with the diode, the parameter  $J_S$  is highly temperature dependent

$$\mathbf{J}_{s} = \mathbf{J}_{sx} \left[ \mathbf{T}^{m} \mathbf{e}^{\frac{-\mathbf{V}_{go}}{\mathbf{V}_{t}}} \right]$$

Typical values for parameters:  $J_{SX}=20\text{mA/}\mu^2$ ,  $V_{G0}=1.17\text{V}$ , m=2.3

The parameter  $\beta$  is also somewhat temperature dependent but much weaker temperature dependence than  $J_{SX}$ .

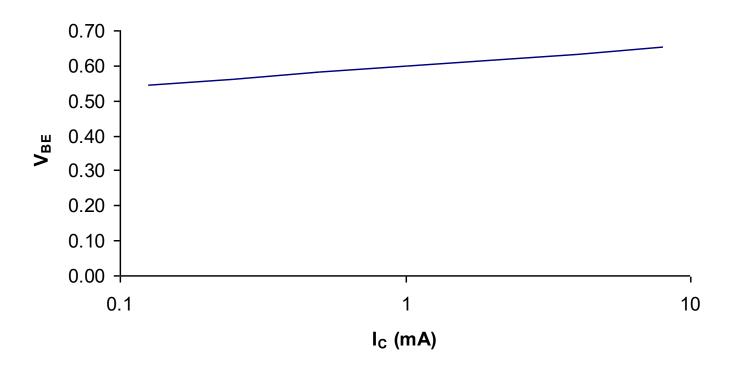

#### **Transfer Characteristics**

npn transistor – Forward Active Operation

$$J_S = .25fA/u^2$$

$A_E = 400u^2$

$V_{\text{BE}}$  close to 0.6V for a two decade change in  $I_{\text{C}}$  around 1mA

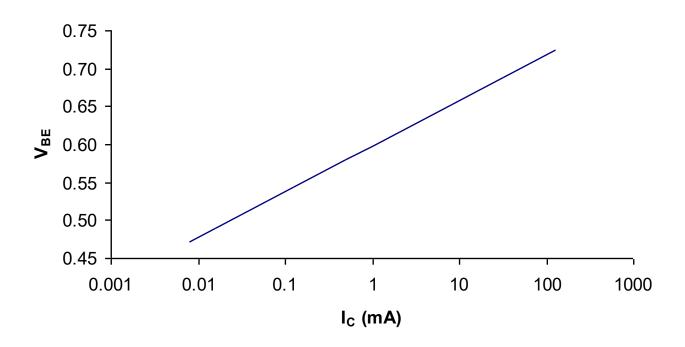

#### **Transfer Characteristics**

#### npn transistor – Forward Active Operation

$$J_S = .25fA/u^2$$

$A_E = 400u^2$

V<sub>BE</sub> close to 0.6V for a four decade change in I<sub>C</sub> around 1mA

npn transistor - Forward Active Operation

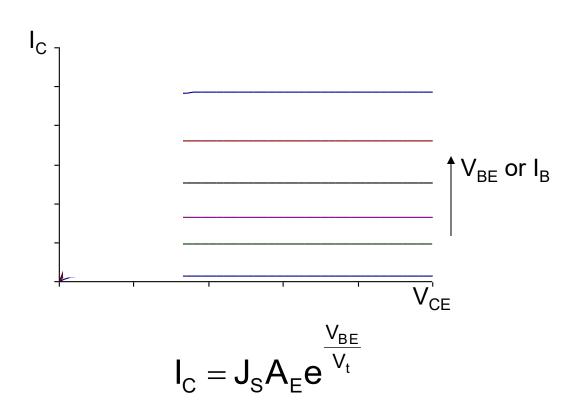

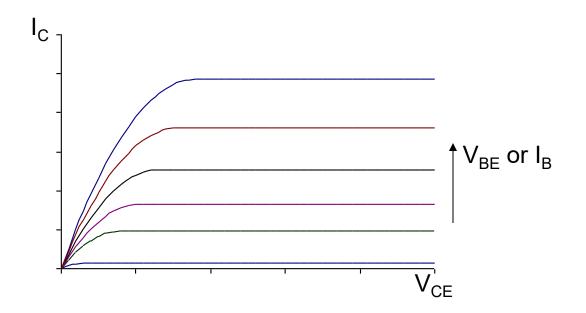

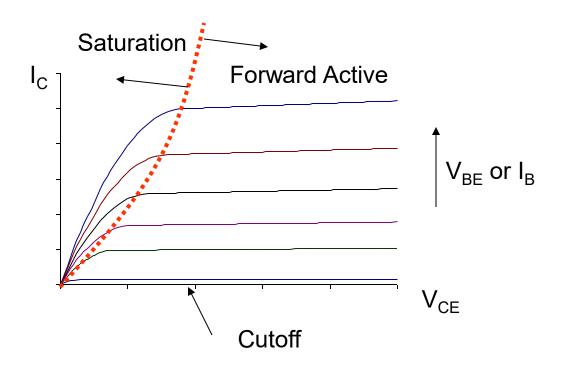

**Output Characteristics**

**Better Model of Output Characteristics**

**Typical Output Characteristics**

Forward Active region of BJT is analogous to Saturation region of MOSFET Saturation region of BJT is analogous to Triode region of MOSFET

Stay Safe and Stay Healthy!

#### End of Lecture 19